- 您现在的位置:买卖IC网 > Sheet目录1250 > TURBO-DECO-XM-UT3 (Lattice Semiconductor Corporation)SITE LICENSE TURBO DECODER XP

�� �

�

Lattice� Semiconductor�

�Turbo� Decoder� User’s� Guide�

�Lattice� provides� a� Turbo� Decoder� IP� core� that� is� both� ?exible� and� compliant� with� three� different� standards:� 3GPP,�

�3GPP2� and� CCSDS.� 3GPP� is� widely� used� in� WCDMA� and� MC-CDMA� applications� while� CCSDS� is� most� com-�

�monly� found� in� telemetry� and� space� communications.� Figure� 1� shows� the� top-level� block� diagram� of� this� core.�

�Lattice� also� supplies� a� Turbo� Encoder� core� that� provides� a� complete� state-of-the-art� error� correction� solution.�

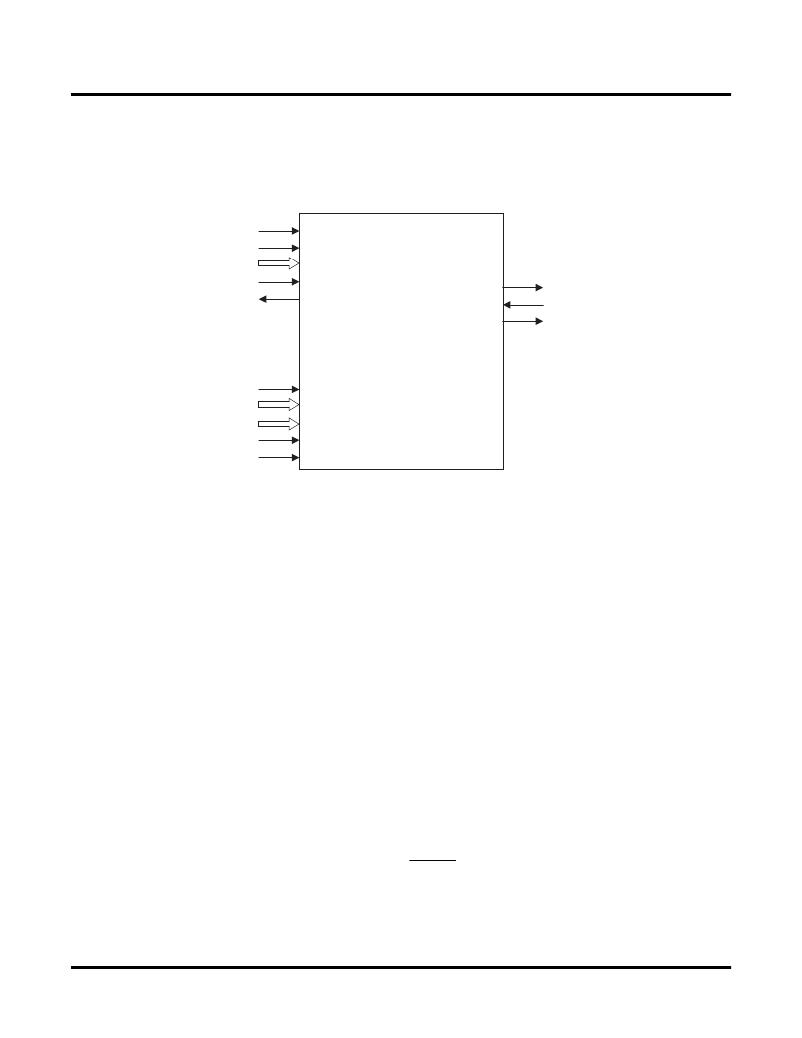

�Figure� 1.� Turbo� Decoder� I/O� Block� Diagram�

�rstn�

�sr�

�din�

�inpvalid�

�rfi�

�dout�

�rfno�

�rfo�

�Turbo�

�Decoder�

�blocksizeset(ipcfgset)�

�blocksize�

�iterations�

�clk�

�rate�

�Note:� Additional� I/O� signals� are� required� if� either� an� external� memory� or� double� buffer� is� selected.� Please� refer� to�

�the� Additional� Signals� for� External� Memory� section� of� this� document� for� further� information.�

�MAP� Algorithm�

�Turbo� decoding� is� based� on� the� principle� of� comparing� the� probability� of� a� received� soft� input� data� being� a� ‘1’� and�

�‘0’.� The� Lattice� Turbo� Decoder� uses� a� decoding� scheme� called� the� MAP� -� Maximum� Aposteriori� Probability� algo-�

�rithm.� The� algorithm� determines� the� probability� of� whether� each� received� data� symbol� is� a� ‘1’� as� well� as� ‘0’.� This� is�

�done� with� the� help� of� the� data,� parity� symbols,� and� the� decoder� knowledge� of� the� encoder� trellis.� A� trellis� is� a� form�

�of� a� state� transition� table� of� the� encoder� input/output.� Based� on� the� data� and� parity� information,� the� MAP� decoder�

�computes� the� probability� of� the� encoder� being� in� a� particular� state.� Depending� on� the� soft� data,� parity� value� and� the�

�weight� from� the� previous� state,� the� probability� that� the� data� is� a� ‘1’� or� ‘0’� can� be� computed.� The� MAP� decoder� com-�

�putes� the� weight� for� each� data� symbol� in� a� given� block� for� both� the� forward� and� reverse� direction.� This� results� in� the�

�computation� of� a� forward� and� reverse� metric.� Using� these� two� values,� the� probabilities� are� computed.� After� the�

�probabilities� are� determined,� they� are� compared� and� a� decision� is� made.� The� Lattice� Turbo� Decoder� IP� core� uses�

�the� logarithm� of� the� probability� to� reduce� computation;� this� is� known� as� Log� Likelihood� ratio� (LLR).� The� computation�

�of� the� probabilities� is� done� iteratively� to� obtain� a� reliable� result.� Once� the� result� is� considered� reliable,� one� can�

�make� a� ?nal� decision� as� to� whether� the� data� symbol� is� a� ‘1’� or� a� ‘0’.� The� Lattice� Turbo� Decoder� can� implement� both�

�the� Log-Map� and� Max-Log-Map� algorithm.� The� Log-Map� algorithm� gives� a� slightly� better� performance� than� the�

�Max-Log-Map� but� utilizes� more� resources� and� runs� at� a� slower� frequency.�

�The� Log� Likelihood� ratio� is� the� probability� that� the� received� data� bit� is� a� ‘0’� divided� by� the� probability� that� the�

�received� data� bit� is� a� ‘1’.�

�L(D)� =� log�

�P (D=0)�

�P� (D=1)�

�The� value� of� L(D)� is� positive� if� P(D=1)� ≤� P(D=)� and� negative� otherwise.� The� output� data� value� is� ‘1’� if� L(D)� is� positive�

�and� ‘0’� if� L(D)� is� negative.� For� one� complete� cycle� of� iteration,� one� needs� to� compute� the� LLR� using� parity� for� non-�

�interleaved� as� well� as� interleaved� data.�

�3�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

TVB058SA-L

SURGE PROTECTOR 58V DO-214AA

TVB200SA-L

SURGE PROTECTOR 200V BREAKOVER

TVB200SC-L

SURGE PROTECTOR 200V BREAKOVER

TVB270SB-L

SURGE PROTECTOR 270V DO-214AA

TVB270SC-L

SURGE PROTECTOR 270V DO-214AA

TVB300SA-L

SURGE PROTECTOR 300V DO-214AA

TVB300SB-L

SURGE PROTECTOR 300V DO-214AA

TVB300SC-L

SURGE PROTECTOR 300V DO-214AA

相关代理商/技术参数

TURBO-DECO-XP-N1

功能描述:编码器、解码器、复用器和解复用器 Turbo Decoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray

TURBO-ENCO-E2-U3

功能描述:编码器、解码器、复用器和解复用器 Turbo Encoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray

TURBO-ENCO-O4-N1

功能描述:编码器、解码器、复用器和解复用器 Turbo Encoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray

TURBO-ENCO-P2-U3

功能描述:编码器、解码器、复用器和解复用器 Turbo Encoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray

TURBO-ENCO-PM-U3

功能描述:开发软件 Turbo Encoder RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

TURBO-ENCO-SC-U3

功能描述:编码器、解码器、复用器和解复用器 Turbo Encoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray

TURBO-ENCO-X2-U3

功能描述:开发软件 Turbo Encoder RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

TURBO-ENCO-X2-UT3

功能描述:开发软件 TURBO ENCODER RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors